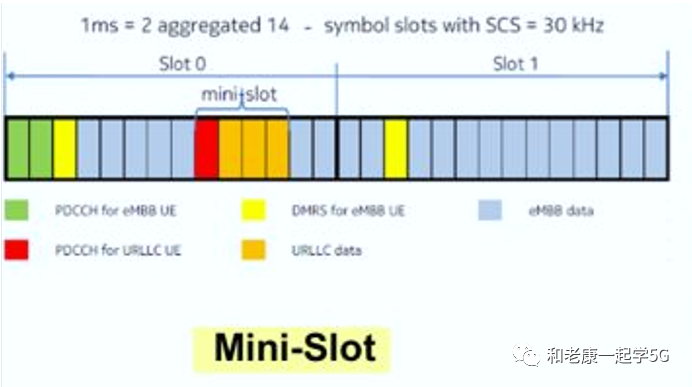

3GPP在5G/NR中将“MiniSlot”定义为承载PDSCH或PUSCH且只有几个OFDM符号长度(2 或4个符号)的时隙,见下图所示。

MiniSlot实现在支持eMTC和URLLC相关规范讨论后,3GPP TR 38.912-8.1中正式定义MiniSlot应用场景如下:

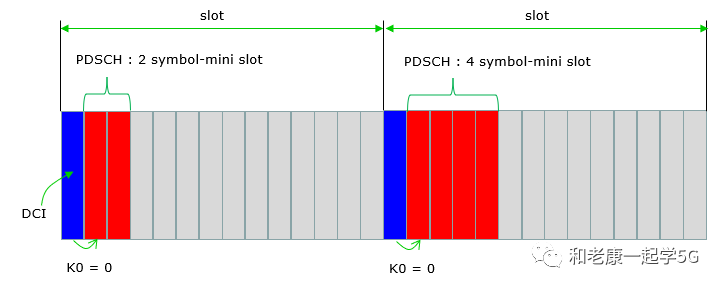

Case1:常规调度

(使用DCI 1_x、DCI 0_x和SLIV)终端和网络在发送一个调度PDSCH的DCI中使用2个或4个OFDM符号(通过SLIV)。DCI(PDSCH)符号直接跟在PDSCH之后。DCI和PDSCH可位于同一时隙(即 K0=0)。

图1.占用2个和4个OFDM符号的MiniSlot

图1.占用2个和4个OFDM符号的MiniSlot 使用

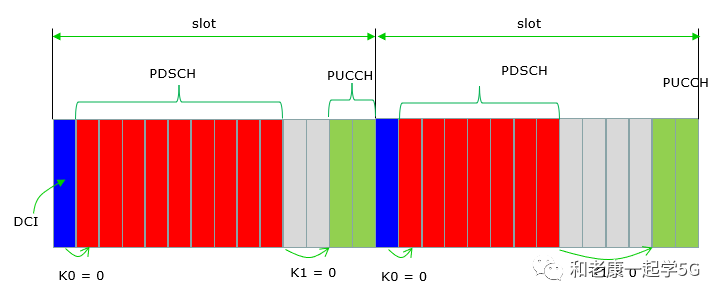

Minislot特殊情况之一是实现携带PDCCH(DL调度),PDSCH(DL数据)、PUCCH(HARQ ACK/NACK)“自包含时隙” 在同一时隙内,这将大大降低物理层延迟。

图2.PDSCH中MiniSlot使用

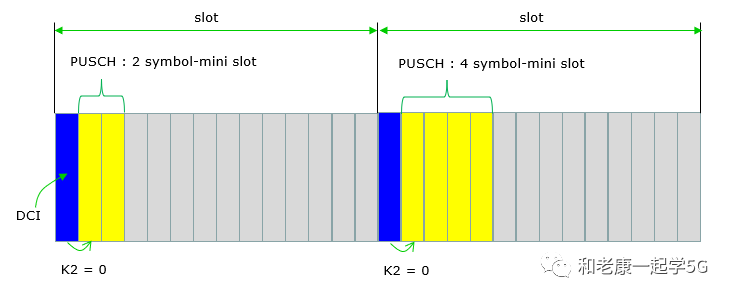

图2.PDSCH中MiniSlot使用 与DL Minislot(PDSCH MiniSlot)一样,可以在上行方向使用UL minislot (PUSCH minislot),发送一个调度PUSCH的DCI使用2个或4个OFDM符号(使用SLIV);DCI(PUSCH)符号直接跟在PUSCH之后,但应用中可在DCI和PUSCH之间放置一个或多个符号间隙,在DL(DCI/PDCCH)和UL(PUSCH)之间切换)没有任何保护期。此外,DCI和PUSCH位于同一时隙(即K2=0)也可以DCI和PUSCH不在同一个时隙(即:K2不为零)的方式调度PDSCH。

图3.PUSCH中MiniSlot使用

图3.PUSCH中MiniSlot使用

Case2:SlotformatCombination和DCI 2_0,另一种方法是从Slotformat Combination中选择一个短符号Slot(如Slotformat 9,17等)并使用DCI 2_0的Slot。

Minislot长度在TR 38.912中描述如下:

长度从1- 2到slot长度;

对于URLLC至少支持2个。

为什么需要Minislot?TR 38.912-8.1中描述如下:

Minislot设计考虑TR 38.912中描述Minislot设计的基线中对于所有其他方面(例如DMRS、HARQ、DL控制、UCI反馈等);Minislot和regular slot之间没有区别。可能发生mini-slot/slot传输占用为相同/不同UE的给定载波正在进行的slot传输调度的资源基于以下情况:

用于Minislot级数据通道的DM-RS只是对时隙级数据通道的复用;

用于Minislot级数据调度的DL控制信道只是对时隙级数据调度的重用;

用于Minislot级UCI反馈的UL控制信道只是对时隙级UCI反馈的重用;

Minislot的调度/HARQ时间线可基于时隙的调度/HARQ时间线;

Minislot的调度/HARQ时间线可基于比时隙更短的调度/HARQ时间线。